Circuit Responses to Radiation-Induced Upsets

- PDF / 429,926 Bytes

- 5 Pages / 612 x 792 pts (letter) Page_size

- 50 Downloads / 280 Views

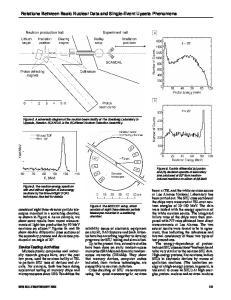

Circuit Responses to Radiation-Induced Upsets Kerry Bernstein Abstract Historically, radiation-induced corruption of data in high-speed complementary metal oxide semiconductor designs has been limited to on-board static random-access memory in various memory caches. Successive generations of scaling, however, have resulted in capacitance reductions in key logic circuits, increasing their vulnerability to these “soft errors.” Charge delivered by radiation events now carries a substantial probability of inducing upsets, not only in bistable elements, but in logic evaluation circuits as well. This article introduces the reader to common logic-circuit topologies in high-speed microprocessors, radiation circuit response mechanisms that can compromise logic evaluation integrity, and existing techniques that mitigate this exposure. Keywords: microelectronics, single-event upsets, soft errors.

Introduction At their heart, microprocessors are state machines. The design of the microprocessor is intended to move a logical system from one state to the next, as defined by the contents of its registers, as quickly as possible. The high-speed circuit topologies found in recent microprocessors update register content by sensing changes in the voltage, current, or, even more simply, the charge present in circuits during an evaluation phase. Hence, it follows that requiring the movement of less voltage, current, or charge to evaluate a logic stage will provide performance advantages. Unfortunately, it also means that increasing circuit performance implicitly makes the circuit more vulnerable to unintended energy sources, such as capacitive or inductive noise, electromotive force, transmission-line reflections, and, now, radiation-induced upsets.1 Soft error susceptibility is strongly dependent upon the response of the materials used, and the concentrations of impurities implanted in them; it is important, then, for material scientists to understand how single-event upsets affect the reliability and behavior of the greater circuit design built in these materials. An upset is a corruption in the logical content of a logic or memory element. The interest of this work is to

126

explore upset mechanisms in high-speed microprocessor logic-circuit families and product designs, aside from those known issues arising from scaled effects in 6-device static random-access memory (SRAM) arrays, the standard 6-transistor SRAM chip. Soft errors in logic are problematic because, unlike techniques such as error-correction coding for memory, there are few remedies for detecting or correcting corrupted logic; we perform the logic operation precisely because we cannot predict the contents of the next machine state. We begin with a description of circuit topologies commonly found in highperformance clocked processors.

fixed interval, as opposed to the two states (“0” or “1”) of a digital device. A phaselocked loop is a precision analog clock on a chip. These circuits each are affected differently by radiation.

Static CMOS Static complementary metal

Data Loading...