CMOS ADCs for Optical Communications

This paper provides a systematic view of ADCs embedded in DSP receivers of coherent optical communications systems. The functionality, performance and CMOS implementation trade-offs are discussed with the focus on techniques achieving high sampling rate a

- PDF / 911,687 Bytes

- 18 Pages / 439.37 x 666.142 pts Page_size

- 48 Downloads / 396 Views

CMOS ADCs for Optical Communications Yuriy M. Greshishchev

Abstract This paper provides a systematic view of ADCs embedded in DSP receivers of coherent optical communications systems. The functionality, performance and CMOS implementation trade-offs are discussed with the focus on techniques achieving high sampling rate and bandwidth. High conversion rate is efficiently addressed by massive interleaving of lower speed SAR ADCs, while the bandwidth limitation is dealt with on both architectural and circuit design levels. In conclusion, results of a 40 Gs/s 6b-ADC implemented in 65 nm CMOS are demonstrated.

6.1

Introduction

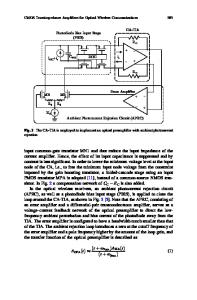

An optical communication receiver for a long time was essentially a single bit data converter with the main amplifier and decision flip-flop in a clock and data recovery circuitry performing the conversion. Signal processing options were limited to analog or analog-digital techniques for example: DFE. Gaining the full DSP functionality was absolutely critical for long haul systems in order to overcome the roadblocks of exponentially growing system cost and the impact of fiber impairments. A 40 Gb/s Dual Polarization (DP) QPSK coherent optical system was the first entry point in the industry, and later became the modulation standard for 40 Gb/s and 100 Gb/s data rates [1]. The 90 nm CMOS DSP ASIC receiver (Fig. 6.1) had four embedded 24 Gs/s 6-b CMOS ADCs with total power of 21 W, of which 25% was consumed by the ADCs [2]. The ADC showed, at the time of announcement, a breakthrough in CMOS speed-power performance at 24 Gs/s, as well as, in power of 6-b SAR converter

Y.M. Greshishchev (*) Ciena Corporation, 3500 Carling Avenue, Ottawa, ON K2H 8E9, Canada e-mail: [email protected] A.H.M. van Roermund et al. (eds.), Nyquist AD Converters, Sensor Interfaces, and Robustness: Advances in Analog Circuit Design, 2012, DOI 10.1007/978-1-4614-4587-6_6, # Springer Science+Business Media New York 2013

97

98

Y.M. Greshishchev

Fig. 6.1 A 40 Gb/s optical DP QPSK Rx ASIC in 90 nm CMOS and embedded ADC performance

used with aggressive interleaved factor of 160 [3]. SAR architecture, traditionally viewed as the slowest, paved the way to the fastest ADC. A similar approach was later used in 65 nm CMOS for sampling rate up to 40 Gs/s [4], and up to 56 Gs/s with 320 SAR converters, but with new sampling technique [5]. The ADC also surpassed the performance of SiGe BiCMOS technology that was viewed as the most suitable option for an optical communication receiver [6].

6.2

DP QPSK Functionality and ADC Requirements

A simplified diagram of a 40 Gb/s DP QPSK receiver is shown in Fig. 6.2 [2]. The optical polarization beam splitter (PBS) segregates the light into two polarization components X,Y, and then each polarization is mixed with the local oscillator (LO) laser. It is converted to quadrature electrical signals I, Q using pin-detectors. A traditional TIA and VGA functionality is followed by the DSP. Each I, Q channel carries approximately a quarter of the bit rate; the symbol rate is 10 Gs/s in the case

Data Loading...