Low Temperature UV Growth of SiO 2 in O 2 and N 2 O

- PDF / 323,008 Bytes

- 6 Pages / 420.48 x 639 pts Page_size

- 19 Downloads / 398 Views

LOW TEMPERATURE UV GROWTH OF SiO 2 IN 02 AND N 20 ASGHAR KAZOR, IAN W. BOYD Electronic & Electrical Engineering UNIVERSITY COLLEGE LONDON Torrington Place, London WC1E 7JE, UK. ABSTRACT We report here the use of a low pressure H& lamp to grow oxide layers on Si in N 2 0 and 02. Layer thicknesses up to 100A, whose IR absorption characteristics are similar to those exhibited by thermal oxides, have been produced. Preliminary modelling of the process is described.

Over the past few decades the minimum feature size in microelectronics (defined as the gate length in the case of an MOS device) has decreased from 10 to 0.7-1.tm while the corresponding gate oxide thicknesses (the SiO 2 layer) have been reduced from 1000 to 250A. It is projected that by the year 2000, chips with 108-109 devices allowing ultra large scale integration (ULSI) will require gate lengths of 0.1-0.25 gm and gate oxide thicknesses of 25-70A +5% [1,2]. As the transition from VLSI to ULSI evolves, there will be an increasing need for reduced temperature processing, so that the thermal budgets for each step of ULSI device processing can be achieved [2]. The thermal budget determines the maximum time allowed for any processing step before dopant redistribution or wafer warpage tolerances are exceeded. For submicron ULSI technology it is measured in seconds and violating these budgets can result in significant reductions in yield. In MOS and DRAM families, which are amongst the most important VLSI technologies, the SiO 2 layer used in the gates and in tunnelling memory structures is usually thermally grown at about 1000°C, where growth rates are of the order of 15A/min [3]. If the temperature is decreased by only a few hundred degrees, the oxidation rate is significantly reduced. For example, at 800 0C, less than IA/min is achieved. During the past few years a number of new low temperature oxidation techniques for MOS technology have been proposed. These include plasma and remote plasma oxidation [4,5] plasma CVD using SiH 4 +N 20 mixtures [61 and Ultra-Violet (UV) oxidation [7,81. Plasma processing often causes the wafer to be bombarded with energetic ions and neutrals which can degrade the electrical characteristics of thin film devices while plasma CVD causes Si reach layer deposition which captures electrons, therefore degrading the electrical properties of the devices [9]. Direct oxidation of the Si surface with UV radiation could overcome some of these problems.

Mat. Res. Soc. Symp. Proc. Vol. 236. 01992 Materials Research Society

372

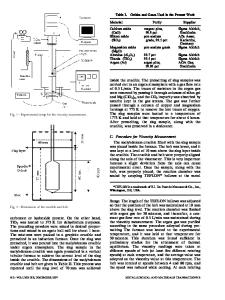

Details of the UV oxidation system used are given elsewhere [101 and are only described very briefly here. The photon source is a 20x20 cm water-cooled low pressure mercury grid lamp. This has a strong UV emission at 254 nm and a weaker one at 185nm, with an intensity ratio of roughly 10:1. The samples used were p-type Si with a resistivity of 2-10 Q cm. Prior to UV exposure they were dipped in HF (48%) and rinsed in de-ionized water. The processing chamber was filled to atmospheric pressure with VLSI grade 02 o

Data Loading...