Optimizing Stressor Film Deposition Sequence in Polish Rate Order for Best Planarization

- PDF / 288,539 Bytes

- 6 Pages / 432 x 648 pts Page_size

- 80 Downloads / 317 Views

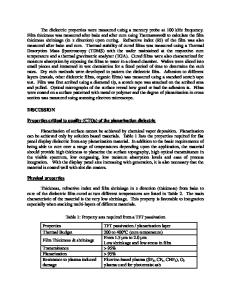

Optimizing Stressor Film Deposition Sequence in Polish Rate Order for Best Planarization John H Zhang1, Changyong Xiao2, Jay W Strane3 , Rajasekhar Venigalla3, Laertis Economikos3, Lindsey Hall1, Jie Chen2, Derek C Stoll3, Jin Wallner3, Haoren Zhuang4, Paul Ferreira1 , Walter Kleemeier1, Cindy Goldberg1, Yongsik Moon2, Connie Truong 3, John Sudijono2, Xiaomeng Chen3, and Ron Sampson1 1

STMicroelectronics, 2070 Route 52, Hopewell Junction, NY 12533, U.S.A. GLOBALFOUNDRIES, 2070 Route 52, Hopewell Junction, NY 12533, U.S.A. 3 IBM Semiconductor Research and Development Center (SRDC), 2070 Route 52, Hopewell Junction, NY 12533, U.S.A. 4 Infineon Technologies, 2070 Route 52, Hopewell Junction, NY 12533, U.S.A 2

ABSTRACT Chemical Mechanical Polish (CMP) is one of the key technologies for the development of modern high performance integrated circuits. The requirements for the CMP uniformity get extremely demanding in order to meet the litho requirements for 32nm technology node and beyond. In this paper, two kinds of orders related to the stressor films that affect the CMP uniformity are revealed. The first is the stressor films deposition order according to the CMP polish rate of each stressor film. The second is the stress gradients order that formed inside the films sitting on top of the stressors. Through the optimization of the order, we show successfully removal of couple hundreds angstroms stressor step heights within 300mm wafer range. The method developed here can also find applications in microelectromechanical systems and 3D integration circuits. INTRODUCTION In material science, stress is an important factor, causing the growth of highly ordered microstructures or the structure cracks. It was reported that the highly ordered microstructures or surface self assembly can happened under the compressive stresses environment[1-4] while the crack growth under tensile stress environment[5-7]. The interfacial stress between different layers [8] and the stress gradient formed under higher pressure [9] and inside films [10] had been studied through various methods. The relationship between carrier mobility and strained layer properties for various materials have been catching a lot of attention in high performance electronic devices[11-13]. In 2004, the international semiconductor development alliance (ISDA) at IBM announced that, for the first time, tensile and compressively stressed nitride contact liners have been simultaneously incorporated into a high performance CMOS flow for 45nm technology node. This dual stress liner (DSL) approach results in NFET/PFET effective drive current enhancement of 15%-32% and saturated drive current enhancement of 11%-20%. Significant hole mobility enhancement of 60% is achieved without using SiGe [14]. In this device, there is an overlap step height of dual stress nitride films stay on the top of the gate as shown Figure1. At 45nm technology node, these kinds of overlap step heights are not a concern

35

due to the high contact open critical dimension (CD). However, when technolog

Data Loading...