Characterization of Local Electrical Property of Coincidence Site Lattice Boundary in Location-controlled Silicon Island

- PDF / 4,042,484 Bytes

- 6 Pages / 612 x 792 pts (letter) Page_size

- 14 Downloads / 293 Views

1025-B16-16

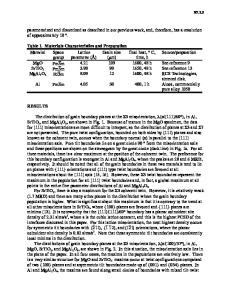

Characterization of Local Electrical Property of Coincidence Site Lattice Boundary in Location-controlled Silicon Islands by Scanning Probe Microscopy N. Matsuki1, R. Ishihara1, A. Baiano1, Y. Hiroshima2, S. Inoue2, and C.I.M. Beenakker1 1 Delft Institute of Microsystems and Nanoelectronics, Delft University of Technology, Feldmannweg 17, Delft, 2628 CT, Netherlands 2 Frontier Device Research Center, SEIKO EPSON Corporation, 281 Fujimi, Fujimi-machi, Suwa-gun, Nagano, 399-0293, Japan ABSTRACT Local electrical property of coincidence site lattice boundaries (CSLBs) in locationcontrolled silicon islands, which are fabricated using µ-Czochralski process (grain filter), was characterized by scanning capacitance microscopy (SCM) and scanning spreading resistance microscopy (SSRM). Some CSLBs found in a silicon island are analyzed as Σ3 and Σ9 by electron back scattering diffraction pattern. These CSLBs are determined as {111}Σ3 and {221}Σ9 by referring to previous observation results made by transmission electron microscopy. {111}Σ3 CSLBs shows no activity for SCM or SSRM; this is consistent with previous prediction that {111}Σ3 CSLB is not electrical active. SCM and SSRM exhibited increase of local capacitance and resistance, respectively, at {221}Σ9 CSLBs. However, the increase is less than that of random boundary. This result implies that {221}Σ9 CSLB has electrical activity, which is less significant than that of the random grain boundaries leading to segregation of dopants or metals. We verified capabilities of SCM and SSRM for characterizing local electrical property of coincident site lattice boundary in silicon. INTRODUCTION It is expected that polycrystalline silicon thin-film transistors (poly-Si TFTs) could be applied to central processing units (CPUs) if the field-effect mobility of the TFT will attain over 500 cm2/Vs with reliable reproducibility and homogeneity. The size of silicon grain obtained by conventional excimer laser annealing (ELA) techniques has stayed less than 1 µm, thus obtained poly-Si TFTs contain a number of random boundaries (RBs) inside the channel, which become critical electrical barriers to make carrier mobility decreased significantly; thus so far development of ELA has been focused on how to enhance the grain size [1-8]. Although the field-effect mobility of TFTs approaches 400 cm2/Vs by lateral growth methods [5-8], there has been large variation in the TFT characteristics owing to inhomogeneous grain size as well as number of existing grain boundaries. In order to solve this problem as well as to realize further enlargement of the grain size as will as controlling the location, we have developed µCzochralski (grain filter) methods [9]. Lateral growth is significantly enhanced due to an effect of grain-filter and the grain size reaches as large as excess of 9 µm on a side and the field-effect mobility approaches 600 cm2/Vs as the average value [10]. Although the random GBs inside the silicon grains are almost all eliminated by this method, still some of special boundari

Data Loading...