Indium-assisted Growth of Si Nanowires: Perspectives on Controlled Growth for CMOS Applications

- PDF / 5,038,251 Bytes

- 6 Pages / 612 x 792 pts (letter) Page_size

- 13 Downloads / 329 Views

1080-O05-01

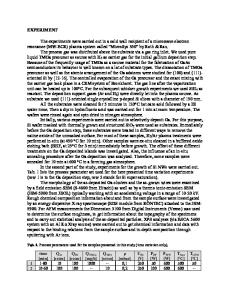

Indium-assisted Growth of Si Nanowires: Perspectives on Controlled Growth for CMOS Applications Francesca Iacopi1, Yann Eichhammer1,2, Claire Massy1, Philippe M Vereecken1, Nele Moelans2, Olivier Richard1, Dries Smeets3, Bart Blanpain2, Stefan De Gendt1,4, and Marc Heyns1,2 1 AMPS, IMEC, Kapeldreef 75, Leuven, 3001, Belgium 2 Metallurgy and Materials Engineering, Katholieke Universiteit Leuven, Leuven, 3001, Belgium 3 Physics, Katholieke Universiteit Leuven, Leuven, 3001, Belgium 4 Chemistry, Katholieke Universiteit Leuven, Leuven, 3001, Belgium ABSTRACT Semiconductor nanowires are attractive nano- building blocks for microelectronics. However, the requirements for their manufacturing and application in the microelectronics industry are very demanding. Beyond compatibility with Si technology, full control on the characteristics of the grown wires (diameter, location, crystallinity, etc..), homogeneity on wafer –scale and reproducibility are essential. In this study we review critically important challenges for a controlled process of In –mediated growth of Si nanowires. First, we stress the importance of surface type for both particle catalysts and growth substrates. Both selection and preparation of such surfaces have large impact on growth, as they influence the initiation and the driving forces for the VLS growth mechanism. Moreover, wire characteristics such as morphology, crystalline quality and growth orientation appear more difficult to control when growing from particles with sizes below 40-50nm. This limitation arises as a result of both fundamental mechanisms and more specific constrains linked to the In-Si system. A few perspectives are given for the achievement of a controlled Si nanowire growth in a Si –technology compatible fashion.

INTRODUCTION Semiconductor nanowires are being considered for microelectronics applications as channel material for vertical devices. The implementation of nanowires building blocks in CMOS technologies would enable the exploration of new architectures on Si [1] and device concepts [2]. We have demonstrated previously that a high yield growth of Si nanowires in a Si –technology compatible fashion can be achieved with the use of In catalyst particles combined to a plasma –enhanced chemical-vapor-deposition (PE CVD) process [3,4]. However, beyond compatibility with Si technology, full control on the characteristics of the grown wires (diameter, location, crystallinity, etc..), homogeneity on wafer –scale and reproducibility are additional and essential requirements for manufacturability of nanowire –based CMOS devices. Also, capability for growing onto foreign substrates needs to be achieved in order to benefit from the possibility of forming devices further away from the Si substrate, i.e. at the interconnects level or at another hierarchy level of the microcircuit. We will indicate that this is overall a rather challenging framework for an unconstrained vapor-liquid-solid (VLS) growth approach. When scaling down the wire diameter towards a few tens of nm and w

Data Loading...