High Integrity SiO 2 /Al 2 O 3 Gate Stack for Normally-off GaN MOSFET

- PDF / 963,120 Bytes

- 6 Pages / 612 x 792 pts (letter) Page_size

- 91 Downloads / 277 Views

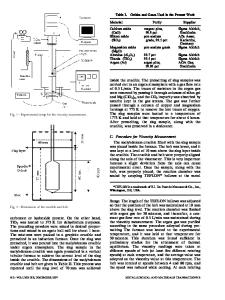

High Integrity SiO2/Al2O3 Gate Stack for Normally-off GaN MOSFET Hiroshi Kambayashi1, 2, Takehiko Nomura1, Hirokazu Ueda3, Katsushige Harada4, Yuichiro Morozumi5, Kazuhide Hasebe4, Akinobu Teramoto2, Shigetoshi Sugawa2, 6 and Tadahiro Ohmi2 1 Advanced Power Device Research Association, Yokohama 220-0073, Japan 2 New Industry Creation Hatchery Center, Tohoku University, Sendai 980-8579, Japan 3 Tokyo Electron Technology Development Institute Inc., Sendai 981-3137, Japan 4 Tokyo Electron Tohoku Ltd., Nirasaki, Yamanashi 407-0192, Japan 5 Tokyo Electron Ltd., Minato-ku, Tokyo 107-6325, Japan 6 Graduate School of Engineering, Tohoku University, Sendai 980-8579, Japan ABSTRACT High integrity SiO2/Al2O3 gate stack has been demonstrated for GaN metal-oxidesemiconductor (MOS) transistors. The SiO2 film formed on GaN by the microwave-excited plasma enhanced chemical vapor deposition (MW-PECVD) exhibits good properties compared that by the LP (Low Pressure)-CVD. Then, by incorporating the advantages of both of SiO2 with a high insulating and Al2O3 with good interface characteristics, the SiO2/Al2O3 gate stack structure has been employed in GaN MOS devices. The structure shows a low interface state density between gate insulator and GaN, a high breakdown field, and a large charge-tobreakdown by applying 3-nm Al2O3. The SiO2/Al2O3 gate stack has also been applied to AlGaN/GaN hybrid MOS heterojunction field-effect transistor (HFET) and the HFET shows excellent properties with the threshold voltage of 4.2 V and the maximum field-effect mobility of 192 cm2/Vs. INTRODUCTION GaN metal-oxide-semiconductor (MOS) field-effect transistors (FETs) with normally-off operation have outstanding features such as being able to operate under high-temperature, highfrequency, and high-power conditions. Therefore, GaN MOSFETs are promising for power switching applications. For GaN MOSFET, a high quality gate insulator is essentially required to be a low interface-state density (Dit) between gate insulator and GaN, a high breakdown voltage and a high reliability, respectively. Both SiO2 and Al2O3 films are good candidates as the gate insulators of GaN MOS transistors since these insulators have large direct wide bandgaps, large conduction band offsets and valence band offsets on GaN, respectively [1]. We have previously reported that the SiO2 formed by Microwave (MW: 2.45 GHz) excited Plasma Enhanced Chemical Vapor Deposition (PECVD) has good properties as the gate insulator for GaN MOS devices compared with that by Capacitive Coupled Plasma (CCP: 13.56 MHz) enhanced CVD. This is because MW plasma is capable of exiting a low-electron temperature (1012 cm-3) at the substrate surface position [2] and the plasma damages, such as ion bombardment and charge-up, are much smaller compared with CCP. However, SiO2 formation by LP (Low Pressure)-CVD, which is a formation process without using plasma, has been reported as the gate insulator of GaN MOS devices [3]. In this work, we have first compared the formation process of SiO2 films between MW-PECVD and L

Data Loading...