Improved Characterization of high-k Degradation with Vacuum C-AFM

- PDF / 308,199 Bytes

- 7 Pages / 612 x 792 pts (letter) Page_size

- 95 Downloads / 295 Views

1074-I11-02

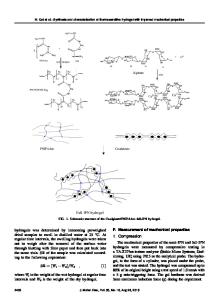

Improved Characterization of high-k Degradation with Vacuum C-AFM Wouter Polspoel1, Wilfried Vandervorst1,2, Lidia Aguilera3, Marc Porti3, Montserrat Nafria3, and Xavier Aymerich3 1 IMEC, Kapeldreef 75, Leuven, 3001, Belgium 2 IKS, KULeuven, Leuven, 3001, Belgium 3 Universidad Autonoma, Barcelona, Spain ABSTRACT Local phenomena like trap assisted tunneling and oxide breakdown (BD) in new high-k gate oxides in advanced MOS devices hinder the acquisition of device requirements stated in the International Technology Roadmap for Semiconductors (ITRS). Conductive Atomic Force Microscopy (C-AFM) visualizes these local phenomena by measuring the local tunneling through the dielectric. In the first part of this work we show that the physical composition of surface protrusions, that are produced at sites electrically stressed with C-AFM and that distort the electrical measurements, is oxidized Si. In the second part, we illustrate that C-AFM measurements become more reliable in high vacuum (1e-5 torr) as surface damage (oxidized Si protrusions) and tip damage are reduced. Finally, we illustrate good agreement between conventional macroscopic electrical measurements and nanometer-scale C-AFM measurements on normal and gate – removed high-k capacitors, respectively. Moreover, to illustrate the strength of the local tunneling technique, we show the possibility of locating BD spots on a highk capacitor.

INTRODUCTION The implementation of new high-k gate oxides in scaled Metal Oxide Semiconductor (MOS) devices demands a profound characterization of these dielectrics. Local (~nm2) phenomena such as trap assisted tunneling and oxide breakdown hinder meeting the device requirements in terms of gate leakage and device lifetime as it is described in the International Technology Roadmap for Semiconductors (ITRS). Generally, the electrical properties of gate dielectrics are investigated with standard macroscopic electrical measurements such as Current – Voltage (I-V), Current – Time (I-t) and Capacitance – Voltage (C-V). Macroscopic refers to the large gate area that averages out local electrical properties. Conductive Atomic Force Microscopy (C-AFM) allows probing these properties at nanometer-scale. Here, a conductive AFM tip in contact with the dielectric surface, acts as a gate of a local MOS stack. Already, this technique has been applied to study charge trapping [1], dielectric degradation [2], and oxide breakdown [3]. However, two main issues currently impede the use of C-AFM as a standard physical and electrical characterization technique for MOS gate oxides. First, this technique is very sensitive to the environment and dielectric surface condition. Surface and tip are easily damaged during measurements. Second, a clear understanding of the correlation between the local leakage behavior observed with C-AFM and the averaged results from standard measurements, is still lacking.

In the first part of this work we investigate the physical composition of surface protrusions that are produced at sites electrically stre

Data Loading...