Polishing Behavior of the Various Interconnect Thin Films in Cu Damascene Process with Different Slurries

- PDF / 266,137 Bytes

- 6 Pages / 612 x 792 pts (letter) Page_size

- 22 Downloads / 324 Views

F6.9.1

POLISHING BEHAVIOR OF THE VARIOUS INTERCONNECT THIN FILMS IN Cu DAMASCENE PROCESS WITH DIFFERENT SLURRIES

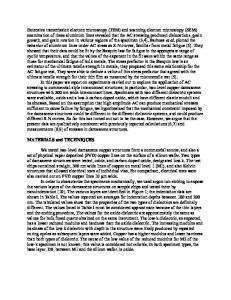

Parshuram B. Zantyea, b, Arun K. Sikderb and Ashok Kumara, b a Department of Mechanical Engineering b Nanomaterials and Nanomanufacturing Research Center University of South Florida, Tampa, FL 33620 c Contact: [email protected] Abstract Chemical Mechanical Polishing is a key technology for Cu damascene wiring process in integrated circuit (IC) manufacturing. It is important to understand the effects of mechanical and tribological properties of the coatings that form a part of Cu damascene structure on the CMP process in order to successfully evaluate and implement these materials. In this paper, we present tribological properties of different interlayer coatings (SiLKTM, Ta and Cu) during their CMP process using different Cu and barrier selective slurries. A micro CMP tester was used to study the fundamental aspects of the CMP process. The coefficient of friction (COF) and acoustic emission (AE) signals were acquired in situ to monitor the process and to see the difference in polishing behavior of these coatings. The issues of end point detection and slurry selectivity are discussed in detail. Introduction The progressive evolution of the Integrated Circuit (IC) has increased the density of active devices on the surface area of the chip. In order to increase the functional density of the IC, the interconnect density must also be increased. RC (Resistance X Capacitance) delay is the most significant determining factor, even more than switching response, which affects the speed of the present day sub 0.5 µm ICs. Thus to minimize the area occupied by the interconnect wiring and to minimize cross talk, multilevel metallization (MLM) schemes with low-k as interlayer dielectric (ILD) need to be implemented. The present day integrated circuits have 6-8 levels of metallization to incorporate multi-functionality on the chip [1]. Fig. 1 shows the schematic of a damascene structure with Cu used as interconnect wiring material, Ta as the barrier and SiLKTM used as the Interlayer dielectric.

Cu (Metal) Ta (Barrier Metal)

SiLKTM (ILD) SiLKTM (ILD)

Cu (Metal)

Fig.1 Schematic representation of a dual damascene structure and its constituents

The polishing of successive layers of coatings in a MLM structure requires excellent slurry selectivity and accurate end point detection of the polishing process. Excessive polishing causes large amount of surface defects like dishing, erosion, wafer to wafer non uniformity (WTWNU) etc. Several innovative approaches like measurement of the change in motor current from the polishing head or the rotating platen [2], approaches like the optical method [3], infra red radiation [4], pad temperature measurement [5], laser beam detection [6], light reflectance analysis [7], and gaseous reactant product detector [8] have been developed as a supplementary module to the actual CMP equipment. The difference in removal rate of one material as compared to another in a particular

Download

Data Loading...