The Effect of the Oxide Interface on the Material and Electrical Properties of Polysilicon Contacts

- PDF / 1,615,251 Bytes

- 7 Pages / 417.6 x 639 pts Page_size

- 69 Downloads / 364 Views

*

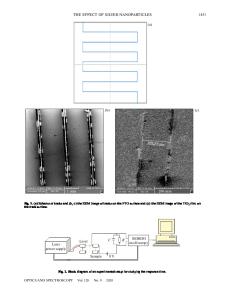

ABSTRACT A strong correlation has been found between the electrical, compositional and structural properties of the polysilicon contact and its interface with the heavily doped polisil-emitter of a transistor. The integrity and thickness of the oxide interface is a major factor for improving the observed performance. Transistors for which the polysilicon was also the diffusion source for the emitter were studied. INTRODUCTION Repeatable device performance is the primary figure-of-merit when considering new designs for digital bipolar transistor applications. At present, the self-aligned polysil-emitter without an interfacial oxide layer is the only viable technology that meets this one criterion. Although the introduction of an interfacial layer results in enhanced current gain, the repeatability criterion cannot be met. The primary reason for this is the conflicting or missing information concerning the role of this interfacial layer in subsequent processing and on carrier transport in the finished transistor [1-4]. The polysilicon-silicon interface is an inextricable part of the overalI self-aligned polysil-emitter design and can not be physically isolated from the rest of the emitter. The interface is completed only after the implantation anneal which is used to activate the dopant species and drive-in the emitter beneath the polysilicon contact. In previous papers [5,6], the authors reported on a capability, using numerical computer simulation to seperate out the base current of the transistor. In this paper, this capability, in conjunction with information taken from TEM cross-sections and a knowledge of the processing, is employed to directly correlate the electrical properties with the structural properties of the polysilicon contact to the transistor. From this correlation, the importance of the interface in determining the grain morphology and defect density as well as in reducing the base current becomes clear. Based on these results, conclusions are then drawn which are relevant to present and future processing of self-aligned polysil-emitter transistors. THE EXPERIMENT Polysi 1icon-Emitter Fabrication A matrix of process steps resulted in fifteen different lots of npn polysil-emitter transistors, with approximately two wafers per lot. The transistors reported on have a common-base and common-collector, fabricated on 3-5 Q-cm n-substrate with a base-col lector junction depth of 1 pm. Emitter windows were opened and a HF dip was completed prior to LPCVD polysilicon deposition. In some cases an intentional thin oxide layer was grown at 680°C for 30 min. prior to polysilicon deposition. From ellipsometer measurements, this was determined to be about 4.5 nm thick.

Mat. Res. Soc. Symp. Proc. Vol. 54.

1986 Materials Research Society

762

The polysilicon was then implanted with phosphorus (at 2 x 101 6 /cm 2 dosage) at 80, 120 or 160 keV and annealed at 900-1000 0 C in order to activate the phosphorous, anneal out the damage, and vary the emitter junction depth. An aluminum contact was deposited over the

Data Loading...