Directed self assembly of nanocrystals within macroscopic to nanoscopic features

- PDF / 1,069,416 Bytes

- 6 Pages / 612 x 792 pts (letter) Page_size

- 111 Downloads / 312 Views

0901-Ra19-03.1

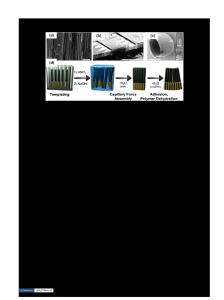

Directed self assembly of nanocrystals within macroscopic to nanoscopic features Scott K. Stanley, Shawn S. Coffee, and John G. Ekerdt Department of Chemical Engineering, The University of Texas at Austin, Austin, TX 78712, U.S.A. ABSTRACT This paper discusses a kinetically-driven patterning scheme to marry top-down and bottomup assembly of nanoparticle arrays. We explain how Ge atoms interact with different dielectric surfaces to either etch the surface or to accumulate and self assemble into nanocrystals during chemical vapor deposition. By exploiting the different reactivity of these dielectrics, the accumulation of adatoms is controlled and thus subsequent self assembly of nanocrystals is controlled. Scanning electron microscopy and atomic force microscopy are used to determine particle densities. We have achieved dense (>1011 cm-2) arrays of self-assembled Ge nanocrystals within ~100 µm sized features (defined by optical lithography) with no Ge deposition on the adjacent SiO2 sacrificial mask region. Electron beam lithography was used to pattern smaller (100 µm to 500 nm) features in which to direct the self assembly. As features shrink below 10 µm, nanoparticle nucleation within the feature is sharply affected. Finally, diblock copolymers are used to pattern 20 nm features to template self assembly of nanoparticles at a scale useful for device applications.

INTRODUCTION Nanomaterials possess great potential to contribute to the electronics industry; however, a major obstacle for applications lies in the difficulty of creating ordered arrays of nanomaterials for use in devices. Flash memory, for example, is well suited for nanomaterials integration. The continuous charge-storing layer in a flash memory device can be replaced by an array of nanocrystals that serve as discrete charge-storage elements [1]. It is well documented in the literature that using nanocrystals in place of a continuous layer results in improved device characteristics for large nanocrystal arrays. For this nanocrystal-based memory to become industrially viable and scalable, we must address the issue of how to reliably arrange the nanocrystals into realistic sized arrays for each device. The nanoparticle array size can be inferred from the international semiconductor roadmap predictions. Using simple geometric considerations (flash memory device with gate length of 180 nm and 5 nm diameter particles at one radius spacing in the gate area) one can calculate that by the year 2010 there will be ~500 particles per device cell. In the year 2018, the number of nanoparticles per device approaches 100 for gate lengths of 120 nm. When dealing with such small numbers of nanoparticles per device, precise positioning of the nanoparticles is mandatory for reliable device performance. The materials systems for this directed self-assembly study are defined by the requirements for a flash memory device. Silicon and Ge nanoparticles are most easily integrated and Ge shows enhanced performance over Si [2]. Additionally, other scaling problems

Data Loading...