Device Structures and Charicterization of one Tansistor Ferroelectric Memory Devices

- PDF / 236,967 Bytes

- 6 Pages / 612 x 792 pts (letter) Page_size

- 93 Downloads / 388 Views

D2.10.1

DEVICE STRUCTURES AND CHARICTERIZATION OF ONE TANSISTOR FERROELECTRIC MEMORY DEVICES Tingkai Li, Sheng Teng Hsu, Bruce Ulrich, Dave Evans Sharp Laboratory of America, Inc. 5700 NW Pacific Rim Blvd. Camas, WA 98607 [email protected]

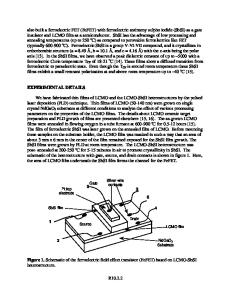

ABSTRACT One-transistor (1T) memory devices with MFIS (Metal, Ferroelectrics, Insulator, Silicon) and MFMIS (Metal, Ferroelectrics, Metal, Insulator, Silicon) structures have been widely studied. These memory devices exhibit memory working functions but very poor retention properties. Three possible mechanisms are responsible for the poor retention of 1 T ferroelectric memories: namely, charges trapping within the gate oxide and ferroelectric film, floating gate effect, and the depolarization field. In order to overcome these problems, a novel ferroelectric transistor design using a semiconductive oxide film in place of the gate dielectric has been fabricated. The device structures are Pt/PGO/InO2/Si (MFSoxS) and Pt/PGO/Ir/InO2/Si (MFMSoxS). There is no insulator in the gate stack. These device structures do not have floating gate and the depolarization field is very low. Therefore, the memory retention time can be very long. In this paper, we report the device structures, integration processes and the working properties with improved retention properties of the Pt/PGO/InO2/Si (MFSoxS) and Pt/PGO/Ir/InO2/Si (MFMSoxS) devices. INTRODUCTION One-transistor (1T) ferroelectric memory devices with MFIS (Metal, Ferroelectrics, Insulator, Semiconductor) and MFMIS (Metal, Ferroelectrics, Metal, Insulator, Semiconductor) structures have been widely studied1-5. These memory devices exhibit memory working functions but very poor retention properties. Three possible mechanisms may be responsible for the poor retention of 1 T ferroelectric memories: namely, leakage current with trapped charge within dielectric and ferroelectric films, floating gate effect, and the depolarization field6. Trapped charges in dielectric and ferroelectric films are due to the high density of internal and interface defects. Trapped charges working together with leakage may affect the retention property. For 1T MFMIS memory devices, when there is a voltage applied across the ferroelectric thin film, there will be current flow in the gate stack, and charges would be trapped in the floating electrode. The trapped charges may neutralize the polarization charges at the interface between the bottom electrode and the ferroelectric film, and could shorten the memory retention time of this structure. The depolarization field applied to the ferroelectric dielectric after programming is due to the existence of an oxide capacitor in series with the ferroelectric capacitor. The linear capacitor tends to discharge all stored charge and therefore, it generates a voltage opposed to the ferroelectric polarization. The depolarization field decreases the initial applied polarization so that finally in time the polarization reaches an intrinsic state. In order to overcome this problem, many scientists have been trying different way to