Impact of sidewall spacer on n-InGaAs devices and hybrid InGaAs/Si CMOS amplifiers in deca-nanometer regime

- PDF / 1,660,754 Bytes

- 8 Pages / 595.276 x 790.866 pts Page_size

- 1 Downloads / 305 Views

TECHNICAL PAPER

Impact of sidewall spacer on n-InGaAs devices and hybrid InGaAs/Si CMOS amplifiers in deca-nanometer regime Suchismita Tewari1 • Suchismita De1 • Abhijit Biswas1 • Abhijit Mallik2 Received: 30 August 2017 / Accepted: 28 November 2017 Ó Springer-Verlag GmbH Germany, part of Springer Nature 2017

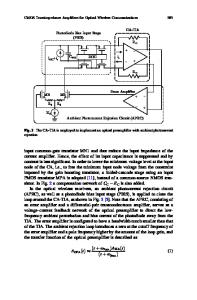

Abstract In this paper, we report, for the first time, the influence of the sidewall spacers (SWS) on the analog performance of InGaAs nMOSFETs at channel lengths of 32 and 22 nm. The study is further extended to the circuit level in which the impact of spacer layer on hybrid CMOSFETs comprising InGaAs nMOSFETs and Si pMOSFETs is thoroughly investigated in analog domain. Using extensive numerical analysis we study the impact of SWS layers on various device parameters e.g., transconductance (gm), transconductance efficiency (gm/ID), output conductance (gd) and intrinsic gain (gm/gd) related to analog applications. Then, the hybrid CMOS current source load amplifier is studied in terms of voltage gain, total capacitance (CTotal) and gain bandwidth product (GBW). The simulation scheme is validated with reported experimental data in the literature. Our findings reveal that all the parameters at the device level, except gd exhibit improved performance for higher value of spacer k. On the contrary, gd decreases with reduced k-value and becomes weakly sensitive to the variation in spacer length (Lsp), for the InGaAs nMOS device having channel lengths (Lg) of 22 and 32 nm. At the circuit level, for the hybrid CMOS amplifier, we found that the dc-gain and CTotal exhibit larger value for higher value of Lsp, while GBW shows higher value for reduced Lsp. Our investigation suggests that improved analog performance of InGaAs nMOSFETs with suitable SWS engineering may be achieved at more advanced technology nodes.

1 Introduction Aggressive device miniaturization in search of enhanced performance over more than four decades, makes III–V semiconductors especially InGaAs as a promising alternative channel material to the conventional Si channel for fabricating nMOSFETs. Research activities on III-V semiconductors, particularly InGaAs, combining high-k gate dielectrics like HfO2, ZrO2, La2O3, etc., have been intensified owing to their augmented electron mobility and injection velocity. The bulk electron mobility in InGaAs can be as high as 15000 cm2/Vs (Lubow et al. 2010; Wu et al. 2009; Lin et al. 2010), resulting in a high drive current for extremely scaled MOSFETs (Koley et al. 2013; Bansal et al. 2004; Tewari et al. 2012, 2013). The high & Suchismita Tewari [email protected] 1

Institute of Radio Physics and Electronics, University of Calcutta, 92 Acharya Prafulla Chandra Road, Kolkata 700009, India

2

Department of Electronic Science, University of Calcutta, 92 Acharya Prafulla Chandra Road, Kolkata 700009, India

electron injection velocity in III-V semiconductors stems from the light carrier effective mass of electrons in such materials. Furthermore, the lower band gap of InGaAs allows lower contact resistance

Data Loading...