Modeling and Simulation of the Influence of SOI Structure on Damage Evolution and Ultra-Shallow Junction Formed by Ge Pr

- PDF / 330,739 Bytes

- 6 Pages / 612 x 792 pts (letter) Page_size

- 70 Downloads / 268 Views

0912-C03-04

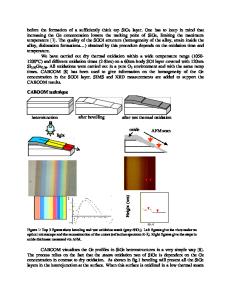

Modeling and Simulation of the Influence of SOI Structure on Damage Evolution and Ultra-Shallow Junction Formed by Ge Preamorphization Implants and Solid Phase Epitaxial Regrowth K. R. C. Mok1, B. Colombeau2, M. Jaraiz3, P. Castrillo3, J. E. Rubio3, R. Pinacho3, M. P. Srinivasan1, F. Benistant2, I. Martin-Bragado4, and J. J. Hamilton5 1 National University of Singapore, Singapore, Singapore, 117576, Singapore 2 Chartered Semiconductor Manufacturing, Singapore, Singapore, 738406, Singapore 3 University of Valladolid, Valladolid, Valladolid, 47011, Spain 4 Synopsys, Mountain View, California, 94043 5 University of Surrey, Guildford, Surrey, GU2 7XH, United Kingdom ABSTRACT Preamorphization implant (PAI) prior to dopant implantation, followed by solid phase epitaxial regrowth (SPER) is of great interest due to its ability to form highly-activated ultrashallow junctions. Coupled with growing interest in the use of silicon-on-insulator (SOI) wafers, modeling and simulating the influence of SOI structure on damage evolution and ultra-shallow junction formation is required. In this work, we use a kinetic Monte Carlo (kMC) simulator to model the different mechanisms involved in the process of ultra-shallow junction formation, including amorphization, recrystallization, defect interaction and evolution, as well as dopantdefect interaction in both bulk silicon and SOI. Simulation results of dopant concentration profiles and dopant activation are in good agreement with experimental data and can provide important insight for optimizing the process in bulk silicon and SOI.

INTRODUCTION Ultra-shallow junction formation by solid phase epitaxial regrowth (SPER) has been shown to be capable of achieving junction characteristics (depth, abruptness, sheet resistance values) that meet the transistor requirements for the 45 nm CMOS node [1]. The technique for the formation of ultra-shallow junctions with boron consists of preamorphizing the substrate prior to dopant implantation, followed by a low temperature SPER process. The amorphous silicon reduces dopant channeling, resulting in abrupt, shallow profiles, while SPER at low temperature, allows only slight diffusion and incorporates dopant atoms into substitutional lattice sites at metastably high concentrations above the equilibrium solid solubility limit [2]. This is an attractive technique as it requires only conventional implant and thermal processing equipment. The use of silicon-on-insulator (SOI) in place of conventional bulk silicon wafers is increasingly popular. SOI offers improved performance and reduced power consumption. Differences in B electrical activation and damage evolution [3] could be expected in the presence of a buried oxide layer, as in the case of SOI, due to the role of oxide interfaces as point defect sinks and the direct correlation between B deactivation and interstitial defect dissolution from the EOR defects [4-7]. It is therefore important to understand and have reliable predictive models to simulate the SPER process and dopant electrical

Data Loading...