Design and Analysis of SRAM cell using Body Bias Controller for Low Power Applications

- PDF / 3,054,335 Bytes

- 24 Pages / 439.37 x 666.142 pts Page_size

- 86 Downloads / 364 Views

Design and Analysis of SRAM cell using Body Bias Controller for Low Power Applications Jitendra Kumar Mishra1 · Bharat Bhushan Upadhyay1 · Prasanna Kumar Misra1 · Manish Goswami1 Received: 4 May 2020 / Revised: 15 October 2020 / Accepted: 17 October 2020 © Springer Science+Business Media, LLC, part of Springer Nature 2020

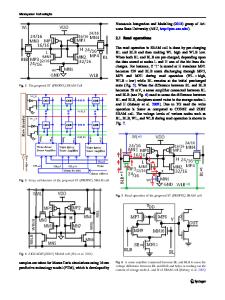

Abstract Low power consumption of electronic devices has become one of the most desirable factors in the present day’s technology. Static random access memory (SRAM) being an integral part of most of the electronic gadget suffers from leakage current which results in static power dissipation and subsequently affects its performance particularly during standby or hold mode. This becomes crucial especially for those systems which are portable and have limited power supply. This work therefore proposes a body bias controller implemented with a 7T SRAM cell at 28 nm CMOS technology node which lowers the static power consumption and increases the hold static noise margin (HSNM) of SRAM during standby mode by changing the threshold voltage. Moreover, it also reduces write delay due to reduction in threshold voltage of proposed design without having a significant effect on write static noise margin and read static noise margin. It has been noticed that there is a reduction of 40%, 28%, 41.9% and 30% in static power dissipation whereas there is an enhancement of 19%, 14.2%, 6.6% and 5.2% in HSNM of the proposed design when compared to 6T SRAM cell, 7T SRAM cell, WRE8T SRAM cell and 9T SRAM cell, respectively. The proposed design can thus be a suitable alternative for low power SRAMs. Keywords Body bias controller · 7T SRAM cell · Static power dissipation · Stability · Delay

B

Manish Goswami [email protected] Jitendra Kumar Mishra [email protected] Bharat Bhushan Upadhyay [email protected] Prasanna Kumar Misra [email protected]

1

Department of Electronics and Communication Engineering, Indian Institute of Information Technology, Allahabad (Prayagraj), India

Circuits, Systems, and Signal Processing

1 Introduction Today’s technologies of electronic devices are the result of “More Moore” which has made the life handy, easy and durable. The main impetus of this is, however, on scaling which was initially proposed by Dennard et al. [6] and whose seed had now cultivated into a fruit. The reduction in dimensions had enabled the designers to place millions of transistors on a single chip. (Surprisingly, the number of transistors in the chip was only 32 when G Moore predicted the law.) However with the scaling of technology node, static power consumption and behavior of transistor as an ideal switch are some of the issues which often become critical and poses problem to the designers. Particularly in memory-based system, power dissipation is a major issues as high density chips have more number of transistors which contribute in overall power dissipation [4]. Moreover, high density of transistors in static random access memory (SRAM) increases the temperature which eventually increases

Data Loading...