Gate-All-Around (GAA) Fully Depleted (FD) Cantilever Channel MOSFET with High-k Dielectric and Metal Gate

- PDF / 492,446 Bytes

- 6 Pages / 612 x 792 pts (letter) Page_size

- 52 Downloads / 396 Views

0995-G05-16

Gate-All-Around (GAA) Fully Depleted (FD) Cantilever Channel MOSFET with High-k Dielectric and Metal Gate Sagnik Dey1, Se-Hoon Lee2, Sachin V. Joshi2, Prashant Majhi3, and Sanjay K. Banerjee2 1 Electrical and Computer Engineering, University of Texas at Austin, Microelectronics Research Center, 10100 Burnet Rd. Bldg #160, Austin, TX, 78758 2 Electrical and Computer Engg, University of Texas at Austin, Austin, TX, 78758 3 Sematech, Austin, TX, 78741

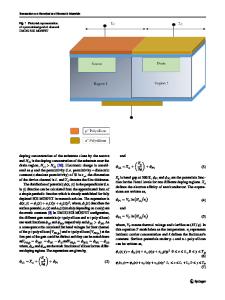

ABSTRACT A MOSFET formed by a Si cantilever channel suspended between source/drain ìanchorsî wrapped all-around by high-κ dielectric and metal gate is demonstrated. The device shows excellent subthreshold characteristics and low leakage currents due to the fully depleted body and the gate-all-around architecture implemented with a high-κ dielectric and metal gate. At the same time this also allows a high drive current due to mobility enhancements arising from the fully depleted cantilever channel such that a large ION/IOFF is achieved. INTRODUCTION As CMOS transistors continue to scale beyond the 45nm nodes, sustaining the historic annual rate of enhancement in performance is becoming increasingly difficult due to several fundamental limitations [1]. While control of leakage currents require gate dielectrics so thin and bodies doped so heavily that a process window sufficiently large for manufacturing might not be found [2]. It might be necessary, therefore, to come up with innovations to augment, if not, replace the conventional CMOS technology to address these challenges. Novel architecture multiple gate MOSFET devices having 3D non-planar geometries have been successfully demonstrated to tackle the electrostatics challenge [3, 4]. Among these, gate-all-around (GAA) architecture devices with the gate surrounding all around the channel have been particularly shown to be an attractive solution for sub 50nm nodes [5]. However as devices are further scaled sustaining acceptable leakage currents and maintaining performance enhancements requires ultra-thin gate dielectrics even for such novel architectures such that conventional SiO2 would need to be replaced by high-κ dielectrics from both manufacturability and gate-oxide-integrity point of view[6]. However a major challenge with a high-κ dielectric MOSFET device is reduced channel mobility. Such mobility degradation has been found to be arising out of Coulomb scattering effects due to increased interface traps[7] along with increased scattering effects associated with the interface excitations of soft surface optical phonon modes and their coupling with surface plasmons [8]. In addition integrating high-κ dielectrics in non planar architectures also becomes a challenge. In this paper we propose a thin body cantilever channel MOSFET architecture surrounded by a high-κ dielectric and metal gate formed by atomic layer deposition (ALD). The GAA architecture of the device leads to excellent suppression of subthreshold leakages and short channel effects due to better gate control and thin body while use of high-κ di

Data Loading...