Electrothermal analysis of novel N-P-P FinFET with electrically doped drain: a dual material gate device for reliable na

- PDF / 1,579,358 Bytes

- 11 Pages / 595.276 x 790.866 pts Page_size

- 3 Downloads / 193 Views

Electrothermal analysis of novel N‑P‑P FinFET with electrically doped drain: a dual material gate device for reliable nanoscale applications Fa. Karimi1 · Zeinab Ramezani2 · I. S. Amiri3,4 · Alireza Mahdavi Nejad5 Received: 20 December 2019 / Accepted: 26 June 2020 © Springer-Verlag GmbH Germany, part of Springer Nature 2020

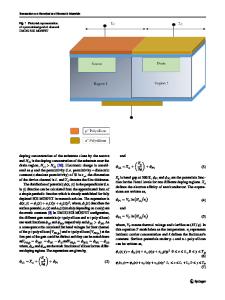

Abstract In this paper, we offer a new structure of N+-P-P Fin Field Effect Transistor (FinFET) with a dual material gate in which the drain side P–N junction has been physically removed. The P-type drain consists of two parts, depletion region (DR) and electrically doped (ED) area, where the ED region is surrounded by an extra gate with optimized length and appropriate work function made of barium (B-gate). The ED region located under the B-gate is converted to N+ drain using the charged plasma (CP) concept to design the CP-FinFET. Improved ability to control the hot carrier effect by amending the critical electric field is the main idea of this work. The p-type depletion region (DR) created between the silicon active layer and electrically doped drain eliminates the gate-drain overlap and reduces the charge sharing and short channel effects (SCE). The modified electric field in the DR region offers advantages including improved hot-electron reliability and high-performance devices. Therefore, in the CP-FinFET the degradation mechanism improves due to the hot carrier effect (HCE) reduction. Indeed, the improvement in device performance is investigated using three-dimensional Atlas simulator with concentrating on the gate current, off-state current, reliability, electron temperature and gate induced drain leakage (GIDL). The comparison results demonstrate the superiority of the proposed structure as a high-efficiency device to design reliable Complementary metal–oxide–semiconductor circuits in nanoscale. Keywords Hot carrier effect · Short channel effect · Gate induced drain leakage · Reliability · FinFET · Charge plasma

1 Introduction * Fa. Karimi [email protected] * I. S. Amiri [email protected] Zeinab Ramezani [email protected] Alireza Mahdavi Nejad [email protected] 1

Department of Electrical Engineering, Pooyesh Institute of Higher Education, Qom, Iran

2

Department of Electrical and Computer Engineering, Northeastern University, Boston, MA 02115, USA

3

Computational Optics Research Group, Advanced Institute of Materials Science, Ton Duc Thang University, Ho Chi Minh City, Vietnam

4

Faculty of Applied Sciences, Ton Duc Thang University, Ho Chi Minh City, Vietnam

5

Department of Interdisciplinary Engineering, Wentworth Institute of Technology, Boston, MA 02115, USA

Multiple gate devices such as Fin field-effect transistors, quadruple gate MOSFETs, double gate devices and gate all around MOSFETs with great electrostatics have shown enormous potential to overcome the CMOS scaling limitations. Increasing the number of gates in SOI devices leads to better control capability over the channel, the improved transconductance, reduced short and

Data Loading...